Семейство однокристальных декодеров EMMA2LL для мультимедийной техники и цифровых абонентских терминаловОдним из основных направлений фирмы RENESAS ELECTRONICS, входящей в японскую корпорацию NIPPON ELECTRONICS COMPANY (NEC), является разработка аппаратных декодеров MPEG-2/H.264 AVС и интегральных схем, предназначенных для применения в бытовой и профессиональной мультимедийной технике. В настоящее время для этого используется оригинальная архитектура EMMA (Enhanced MultiMedia Architecture) третьего поколения, позволяющая максимально интегрировать процесс обработки сжатых изображений ТВ сигналов обеих систем на одном кристалле. Это дает возможность использования создаваемых ИМС для цифровой обработки сигналов стандарта MPEG-2/H.254 в реальном времени и применения их в спутниковых, эфирных, кабельных абонентских приставках, а также в ресиверах, используемых для IP-вещания.

Предыдущее поколение ИМС архитектуры EMMA2 предназначалось для создания однокристальных декодеров для обработки ТВ сигналов, сжатых только по стандарту MPEG-2. В этой статье приводится описание семейства EMMA2LL, созданного на основе архитектуры EMMA2. ИМС семейства получили широкое применение в приставках стандартов DVB-C, DVB-S и DVB-T для приема цифрового ТВ. Оно включает в себя ИМС mPD611106-mPD61112 и mPD61114-mPD61116 с архитектурой MIPS® Core. ИМС нового семейства отличаются только некоторыми функциональными возможностями.

Основные характеристики ИМС семейства EMMA2LL

Все ИМС описываемого семейства имеют двухпроцессорную архитектуру. Основное ядро основано на архитектуре MIPS® 4KEc, созданной фирмой MIPS Technologies. Оно обеспечивает пользовательский интерфейс и функционирование в реальном времени операционной системы. Кроме основного ядра на кристалле ИМС содержится субпроцессорное ядро с архитектурой MIPS® 4KEm для декодирования входного сигнала, основная функция этого ядра — декодирование сжатого сигнала звукового сопровождения. Оба ядра функционируют на частоте 167 МГц с быстродействием 200 MIPS и имеют по два 4 Кбайт кеша команд и данных (Instruction-cache и Data-cashe).

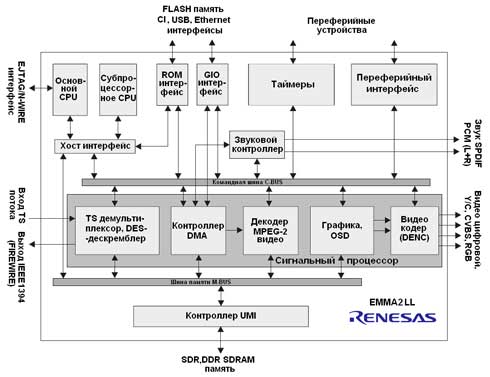

Рис. 1. Блок-схема ИМС семейства mPD6121x

Унифицированный интерфейс памяти UMI (Unifed Memory Interface) поддерживает внешнюю синхронную память SDRAM объемом до 128 Мбайт, работающую на частоте 133 МГц (mPD61111 и mPD61115 работают с DDR-памятью объемом до 64 Мбайт). Внешняя память может использоваться всеми узлами декодера. Для доступа к более медленным устройствам используются ROM/GIO-интерфейсы. Интерфейс ROM позволяет подключать внешнюю NOR/NAND Flash-память объемом до 64 Мбайт. К интерфейсам в хост-режиме также можно подключать PCMCI-слоты для CAM-модулей условного доступа к платным программам.

ИМС семейства EMMA2LL предназначены для работы в приемных системах как спутникового, так и наземного вещания ТВ программ (кабельное и эфирное) стандартной разрешающей способности SD (Standard Defenition). Входные данные транспортного потока TS можно вводить в ИМС в параллельном или последовательном виде со скоростью до 100 Мбит/с. Входной сигнал обрабатывается демультиплексором. Встроенный DES-дескремблер производит декодирование с 16 парами секретных ключей. Декомпрессия изображения осуществляется по стандарту MPEG-2 MP@ML. Все ИМС поддерживают функцию декодирования звука, передаваемого в двух звуковых слоях Layers 1, 2 MPEG-2.

К выходу декомпрессора подключен графический процессор (бит-блиттер), который улучшает качество изображения и обеспечивает наложение экранной графики на основное изображение. Сигнал изображения обрабатывается четырьмя ЦАП и передается на выход в стандартном аналоговом виде, включая врезку дополнительной информации (телетекст, субтитры). ИМС mPD61112 и mPD61116 могут формировать в выходном сигнале вставки системы защиты от копирования MACROVISION 7.1.

ИМС mPD61114—mPD61116 имеют функцию активации защиты от копирования программ, которая доступна только авторизованным клиентам.

На кристалле ИМС также содержится ряд вспомогательных периферийных устройств. Это два асинхронных интерфейса UART, интерфейс I2C, синхронный последовательный интерфейс, два интерфейса для чтения смарт-карт, интерфейс ИК порта, два системных таймера общего назначения, а также сторожевой таймер и часы реального времени.

Функциональное описание ИМС семейства EMMA2LL

Блок-схема ИМС mPD6121x показана на рис. 1. Как было сказано выше, в основе прибора лежит двухпроцессорная архитектура с приоритетным разделением выполняемых функций.

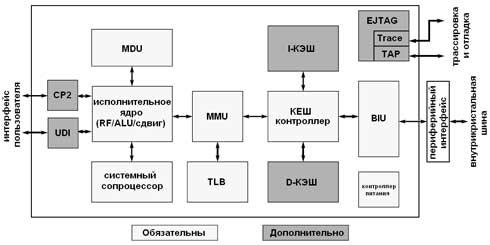

Рис. 2. Блок-схема основного процессорного ядра 4KEc

Основное процессорное ядро — 4KEc (код разработчика JADE), его блок-схема показана на рис. 2. Ядро входит в семейство 32-битных RISC-процессоров 4KE для пользовательских встраиваемых приложений. Оно имеет низкое энергопотребление и специально разрабатывалось для компаний-производителей полупроводниковых ИМС, разработчиков ASIC ИМС и OEM-систем.

Статья доступна только в печатном варианте. Вы можете приобрести свежие номера Р&С или оформить подписку в редакции. |